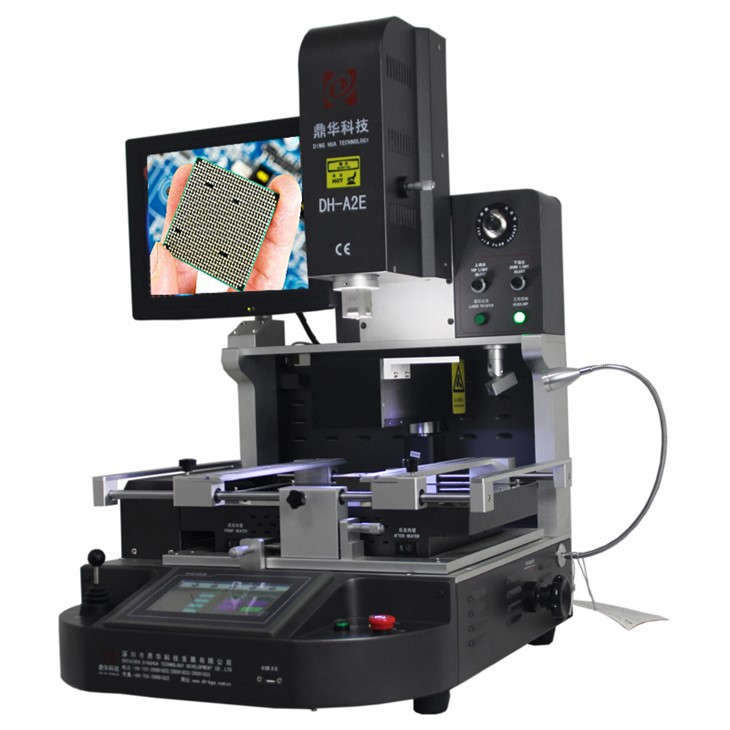

Auto Optical BGA Rework Station

Weit verbreitet bei der Reparatur auf Chipebene für Motherboards von Mobiltelefonen, Laptops, Computern, Fernsehern, Klimaanlagen usw. Es hat eine hohe Reparaturerfolgsrate und einen hohen Automatisierungsgrad und spart viel menschliche Mühe. Wir sind professioneller Hersteller dieser Maschine und haben diese Maschinen auf Lager.

Beschreibung

Auto Optical BGA Rework Station

1. Anwendung der Auto Optical BGA Rework Station

Motherboard von Computer, Smartphone, Laptop, MacBook-Logikplatine, Digitalkamera, Klimaanlage, Fernseher und anderer Elektronik

Ausrüstungen aus der medizinischen Industrie, Kommunikationsindustrie, Automobilindustrie usw.

Geeignet für verschiedene Arten von Chips: BGA, PGA, POP, BQFP, QFN, SOT223, PLCC, TQFP, TDFN, TSOP, PBGA, CPGA, LED-Chip.

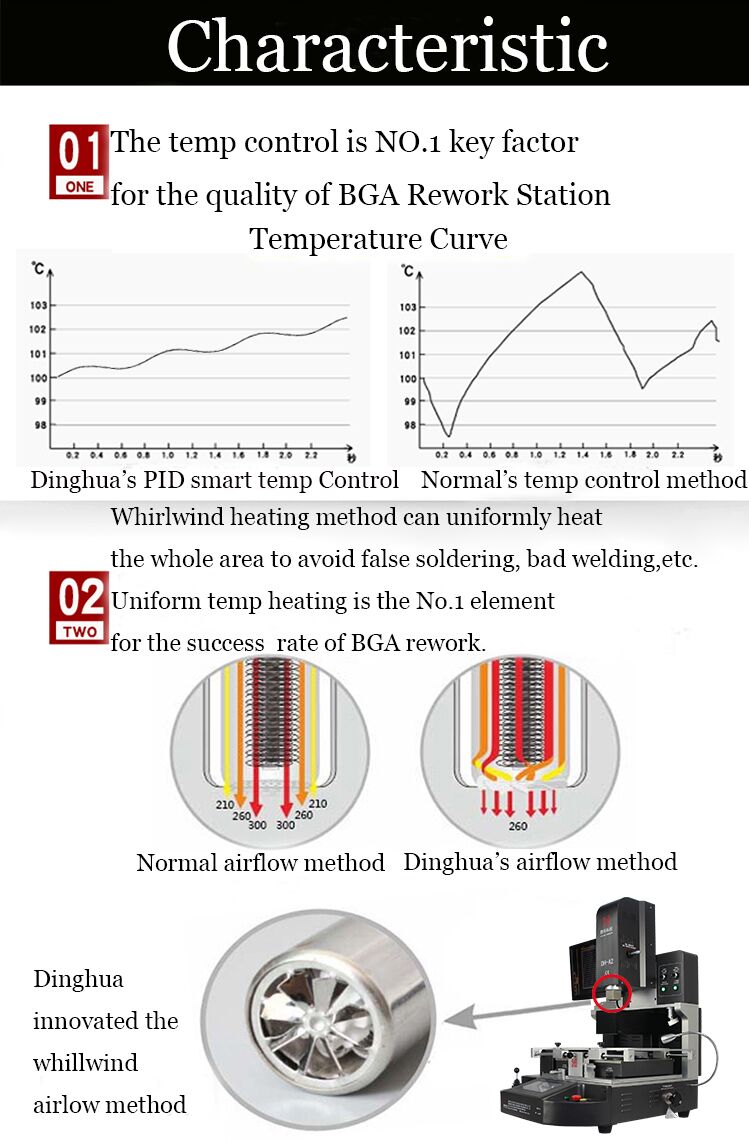

2.Produktmerkmale der Auto Optical BGA Rework Station

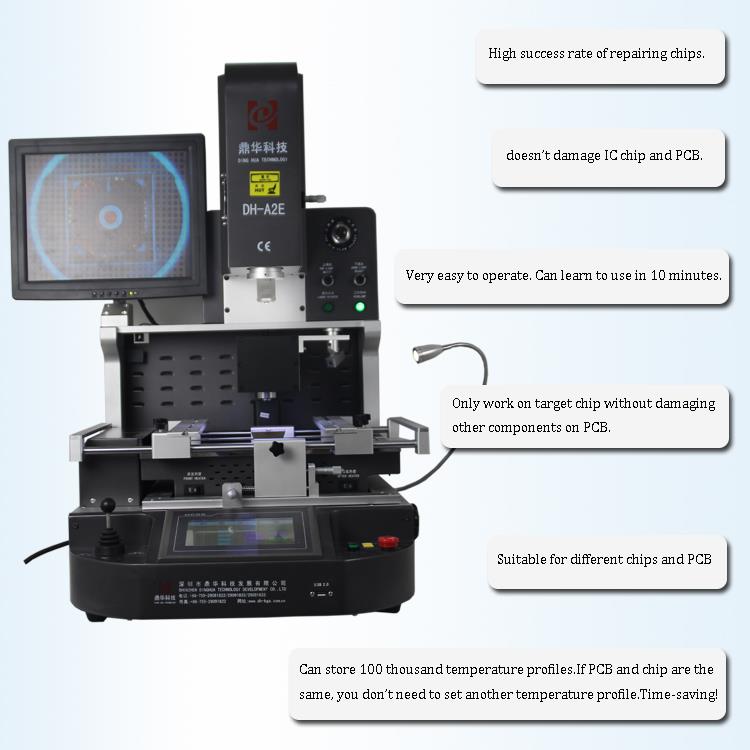

•Hohe Erfolgsquote bei Reparaturen auf Chipebene. Der Entlöt-, Montage- und Lötprozess erfolgt automatisch.

• Präzise Ausrichtung jeder Lötstelle kann mit optischer Ausrichtungs-CCD-Kamera garantiert werden.

•Präzise Temperaturregelung kann mit 3 unabhängigen Heizzonen sichergestellt werden. Die Maschine kann einstellen und speichern

1 Million Temperaturprofil.

• Das eingebaute Vakuum im Montagekopf nimmt den BGA-Chip automatisch auf, nachdem das Entlöten abgeschlossen ist.

3. Spezifikation der automatischen optischen BGA-Überarbeitungsstation

4.Details der automatischen optischen BGA-Überarbeitungsstation

CCD-Kamera (präzises optisches Ausrichtungssystem); 2. HD-Digitalanzeige; 3. Mikrometer (Spanwinkel einstellen);

4.3 Standheizungen ( Heißluft & Infrarot ) ; 5. Laserpositionierung; 6. HD-Touchscreen-Schnittstelle, SPS-Steuerung;

7.LED-Scheinwerfer; 8.Joystick-Steuerung.

5.Warum sollten Sie sich für unsere automatische optische BGA-Überarbeitungsstation entscheiden?

6. Zertifikat der automatischen optischen BGA-Überarbeitungsstation

7. Verpackung und Versand der Auto Optical BGA Rework Station

8.Häufig gestellte Fragen

Wie teste ich den Chip?

Erster Chiptest auf Systemebene

Das SoC basiert auf Prozessen im tiefen Submikrometerbereich, sodass das Testen neuer Soc-Geräte einen völlig neuen Ansatz erfordert. Denn jede funktionale Komponente

eigene Testanforderungen hat, muss der Konstrukteur früh im Designprozess einen Testplan erstellen.

Der Block-für-Block-Testplan für SoC-Geräte muss implementiert werden: ordnungsgemäß konfigurierte ATPG-Tools für Logiktests; kurze Prüfzeiten; neue Hochgeschwindigkeit

Fehlermodelle und mehrere Speicher- oder kleine Array-Tests. Für die Produktionslinie findet das Diagnoseverfahren nicht nur den Fehler, sondern trennt ihn auch

fehlerhafter Knoten vom funktionierenden Knoten. Außerdem sollten, wann immer möglich, Test-Multiplexing-Techniken verwendet werden, um Testzeit zu sparen. Im Bereich hoch

integrierte IC-Tests, ATPG und IDDQs testbare Designtechniken verfügen über einen leistungsstarken Fehlertrennungsmechanismus.

Andere tatsächliche Parameter, die im Voraus geplant werden müssen, sind die Anzahl der zu scannenden Pins und die Größe des Speichers an jedem Pin-Ende.

Boundary Scans können auf dem SoC eingebettet werden, sind aber nicht auf Verbindungstests auf Platinen oder Multi-Chip-Modulen beschränkt.

Obwohl die Chipgröße abnimmt, kann ein Chip immer noch Millionen bis 100 Millionen Transistoren packen, und die Anzahl der Testmodi ist auf ein beispielloses Niveau gestiegen

Niveaus, was zu längeren Testzyklen führt. Dieses Problem kann getestet werden. Moduskomprimierung zu lösen, kann das Komprimierungsverhältnis 20 Prozent bis 60 Prozent erreichen. Für die heutige Großserie

Chipdesign, um Kapazitätsprobleme zu vermeiden, ist es notwendig, Testsoftware zu finden, die auf 64-Bit-Betriebssystemen ausgeführt werden kann.

Darüber hinaus ist Testsoftware mit neuen Testproblemen konfrontiert, die durch tiefe Submikron-Prozesse und zunehmende Häufigkeit verursacht werden. In der Vergangenheit war der ATPG-Testmodus für

das Testen von statischen Blockierungsfehlern war nicht mehr anwendbar. Das Hinzufügen von funktionalen Mustern zu herkömmlichen Werkzeugen machte es schwierig, neue Fehler zu finden. Ein besserer Ansatz ist

Klassifizieren Sie frühere Funktionsmodusgruppen, um zu bestimmen, welche Fehler nicht erkannt werden können, und erstellen Sie dann einen ATPG-Modus, um diese fehlenden Fehlertypen zu erfassen.

Wenn die Designkapazität zunimmt und die Testzeit pro Transistor abnimmt, um geschwindigkeitsbezogene Probleme zu finden und das Schaltungs-Timing zu überprüfen, wird ein synchrones Testverfahren verwendet

beschäftigt werden müssen. Synchrones Testen muss mehrere Fehlermodelle beinhalten, einschließlich transienter Modelle, Pfadverzögerungen und IDDQ.

Einige Unternehmen in der Branche glauben, dass die Kombination von Blockierungs-, Funktions- und Übergangs-/Pfadverzögerungsfehlern die effektivste Teststrategie sein kann. Für tief

Submikron-Chips und Hochfrequenzbetrieb, Transienten- und Pfadverzögerungstests sind sogar noch wichtiger.

Um das Problem der ATE-Genauigkeit beim Synchronisieren des Testkerns zu lösen und die Kosten zu reduzieren, ist es notwendig, ein neues Verfahren zu finden, das die Schnittstelle vereinfacht

das Testgerät (Transienten- und Pfadverzögerungstest erfordern einen genauen Takt an der Schnittstelle des Testgeräts). Es stellt sicher, dass das Signal während des Tests genau genug ist.

Da eine hohe Wahrscheinlichkeit von Herstellungsfehlern im SoC-Speicherblock besteht, muss der Speicher-BIST eine Diagnosefunktion haben. Sobald ein Problem gefunden wird,

die defekte Adresseinheit kann auf den redundanten Speicher der Ersatzadresseinheit abgebildet werden, und die erfasste Fehleradresse wird verworfen. Wegwerfen vermeiden

der ganze teure Chip.

Das Testen kleiner eingebetteter Speicherblöcke macht zusätzliche Gatter oder Steuerlogik überflüssig. Zum Beispiel können Vektorumwandlungstesttechniken umwandeln

Funktionsmodi in eine Reihe von Scanmodi.

Im Gegensatz zum BIST-Verfahren erfordert der funktionale Eingang des Bypass-Speicherblocks keine zusätzliche Logik. Da keine zusätzliche Testlogik erforderlich ist, bietet SoC

Entwicklungsingenieure können in der Vergangenheit erstellte Testmuster wiederverwenden.

Fortgeschrittene ATPG-Tools testen Makros nicht nur parallel, sondern stellen auch fest, ob es Konflikte gibt, und geben detailliert an, welche Makros parallel getestet werden können und welche

Makros können nicht parallel getestet werden. Außerdem können diese Makros effektiv getestet werden, selbst wenn der Makrotakt derselbe ist wie der Abtasttakt (z. B. synchroner Speicher).

Derzeit gibt es auf der dichten doppelseitigen Platine nicht genügend Testpunkte, und jeder komplexe Chip muss mit einer Boundary-Scan-Schaltung ausgestattet werden. Ohne

Boundary Scans und die Suche nach Herstellungsfehlern auf Platinenebene sind ziemlich schwierig und können nicht einmal gefunden werden. Mit Boundary Scan ist das Testen auf Platinenebene extrem einfach

und unabhängig von der Logikschaltung innerhalb des Chips. Boundary Scan kann auch den ATPG-Modus in jeder Phase der Produktion an die Scan-Kette des Chips konfigurieren.